あなたは平成22年10月20日以来

人目のお客様です

もくじ

|

MOS-FETの書き方とモデルの設定

1.FETそのものの書き方

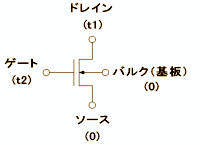

m番号 ドレイン端子 ゲート端子 ソース端子 バルク(基板)端子 モデル名

+ l=ゲート長 w=ゲート幅 ・・・他いろんな設定

(いろいろあります、本で調べてみて下さい)

(例 mn2 t1 t2 0 0 nm l=4u w=8u ad=80p as=80p pd=36u ps=36u )

2.素子モデル設定の書き方

.model モデル名 種別(nmos 又は pmos)(level=1 vto=しきい値 tox=ゲート酸化膜厚 ・・・他いろんな設定)

(例.model nm nmos (level=2 vto=1.0 tox=0.035u nsub=1e16 uo=500

+ucrit=4.5e4 ・・・) )

エンハンスメント型MOSとディプリッション型MOSの書き分けはしきい値(vto)の設定で書き分けます。

実際に使用する素子のモデルパラメーターを使用したい場合はメーカーのホームページを調べると見つかることがあります。また、ホームページ上になくてもメーカーや代理店に問い合わせるともらえる時があります。ただし、TO-92パッケージのように足を加工できるような部品の場合、足の加工により等価回路が変わるためそのままの等価回路の入手ができない場合もあります。

例:NEC 2SC3355 (TO-92) のモデルパラメーターは入手不可だが同チップ表面実装品の 2SC3357 のモデルパラメーターは入手可能

一方で、有志の手により真 空 管の回路モデルが作られ配布されていたりします。

|

※注意・バルク(基盤)の接続について

バルクの端子は、通常、NMOSは回路中の最も電位の低いところに接続し、PMOSは回路中の最も電位が高い端子に接続します。バルクについての記述がない場合には、ソース側(これはNMOS・PMOSとも同じ)に接続されているものと見なされます。でも、それでは逆方向に電流が流せないのでメモリの読み出し・書き込み制御用トランジスタのような両方向に電流が流れるような場合にはバルクは必ず設定してください。

|

|

|